For Verilog and VHDL hardware design language notes and examples. Questions can be asked and can be answered by readers or authors. Technical EDA tools information should be provided. Info is provided with no verification and can be used freely at reader's own risk.

Monday, August 22, 2016

Advanced Usage of Verilog Date Types

a) Physical data type

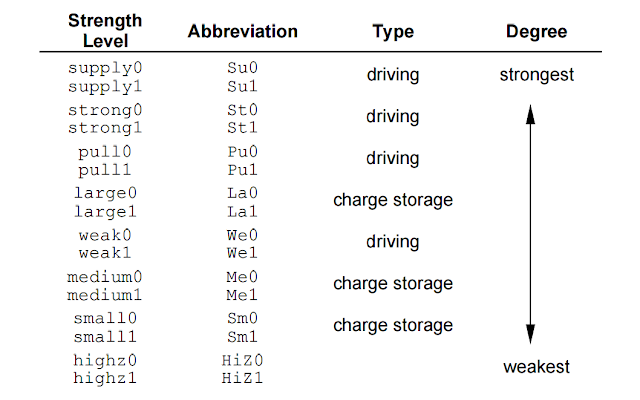

• Net (wire, wand, wor, tri, triand, trior). Default value is z. Used mainly in structural modeling.

• Register (reg). Default value is x. Used in dataflow/RTL and behavioral modelings.

• Charge storage node (trireg). Default value is x. Used in gate-level and switchlevel modelings.

b) Abstract data type — used only in behavioral modeling and test fixture.

• Integer (integer) stores 32-bit signed quantity.

• Time (time) stores 64-bit unsigned quantity from system task $time.

• Real (real) stores floating-point quantity.

• Parameter (parameter) substitutes constant.

• Event (event) is only name reference — does not hold value.

Examples:

4'b1011 // 4-bit binary of value 1011

234 // 3-digit decimal of value 234

2'h5a // 2-digit (8-bit) hexadecimal of value 5A

3'o671 // 3-digit (9-bit) octal of value 671

4b'1x0z // 4-bit binary. 2nd MSB is unknown. LSB is Hi-Z.

3.14 // Floating point

1.28e5 // Scientific notation

Subscribe to:

Post Comments (Atom)

No comments:

Post a Comment