Language for CHIP design

For Verilog and VHDL hardware design language notes and examples. Questions can be asked and can be answered by readers or authors. Technical EDA tools information should be provided. Info is provided with no verification and can be used freely at reader's own risk.

Tuesday, August 1, 2023

Very simple I2C monitor for digital simulation in Verilog

Wednesday, August 24, 2016

Free Online Digital Diagram Generator No login required

USE WINDOWS IE TO DRAW A SHARPER IMAGE

This is a free online digital diagram drawing program. Free to use and no login required.

Use simple text symbols (case sensitive) to specify the drawing mode of the diagram in text boxes. 7 digital traces can be shown in each diagram. Simple rules are specified below and in the example tutorial.

Signal: Support Signal name, 0 ->logic low, 1 ->logic high, Z ->high Impedance

Bus: Support Bus Name, H ->value high, L ->value low, Z -> high Impedance, X ->unknown

Marker: Specified with symbol M

Notation: Marked in between two single quotes

Save Options

1. Update the drawing then click and bookmark the link.

2. Update the drawing then "Right Click" the link and select "copy link". Then you can past the link in your email, documents, browser, and etc.

3. Update the drawing then use WIN10 snipping tool or "Print Screen" key to capture the display. Then save it to an image file.

4. Use your phone to take a picture of the diagram.

Tuesday, August 23, 2016

An Example of Verilog Sync RAM

// Synch. RAM 32x256

// INTEL MICRO CORP

module DPRAM (

input wire mem_clk, // RTL RAM clock

input wire [7:0] wrAddr,

input wire [31:0] dprIn,

input wire dprWe, // Write enable

input wire [7:0] rdAddr,

output reg [31:0] dprOut

);

reg [31:0] memArray [0:255];

always @ (posedge mem_clk) begin

if(dprWe) memArray[wrAddr] <= dprIn;

dprOut <= memArray[rdAddr];

end

endmodule

Monday, August 22, 2016

Note About Using Verilog Task and Functions

- Both tasks and functions are defined locally in the module in which the tasks and functions will be invoked.

- No initial or always statement may be defined within either tasks or functions.

- Tasks and functions are different — task may have 0 or more arguments of type input, output or inout ; function must have at least one input argument.

- Tasks do not return value but pass values through output and inout arguments; functions always return a single value, but cannot have output or inout arguments.

- Tasks may contain delay, event or timing control statements; functions may not.

- Tasks can invoke other tasks and functions; functions can only invoke other functions, but not tasks.

module TestTop;

reg [1:0] r1;

reg [3:0] r2;

reg r3;

initial begin

r1 = 2'b01;

r2 = myFunc(r1); // Invoke function

$display("r2 = %b", r2);

myTask (r2, r3); // Invoke task

$display("myTask return = %d",r3);

end

task myTask;

input [3:0] i;

output myTaskOut;

begin

#10;

myTaskOut = (i == 4'b0101);

end

endtask

function [3:0] myFunc;

input [1:0] i;

begin

myFunc = {i,i}; // Return value

end

endfunction

endmodule

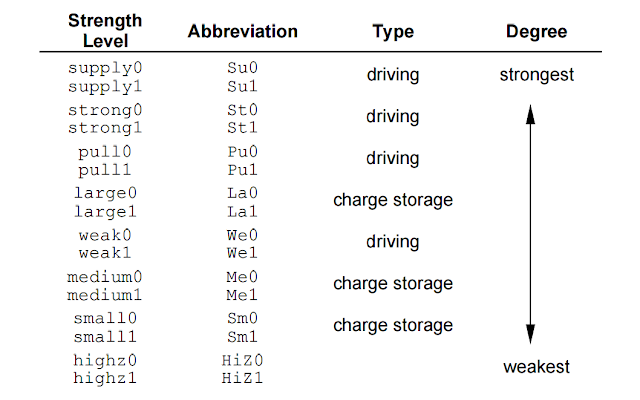

Advanced Usage of Verilog Date Types

a) Physical data type

• Net (wire, wand, wor, tri, triand, trior). Default value is z. Used mainly in structural modeling.

• Register (reg). Default value is x. Used in dataflow/RTL and behavioral modelings.

• Charge storage node (trireg). Default value is x. Used in gate-level and switchlevel modelings.

b) Abstract data type — used only in behavioral modeling and test fixture.

• Integer (integer) stores 32-bit signed quantity.

• Time (time) stores 64-bit unsigned quantity from system task $time.

• Real (real) stores floating-point quantity.

• Parameter (parameter) substitutes constant.

• Event (event) is only name reference — does not hold value.

Examples:

4'b1011 // 4-bit binary of value 1011

234 // 3-digit decimal of value 234

2'h5a // 2-digit (8-bit) hexadecimal of value 5A

3'o671 // 3-digit (9-bit) octal of value 671

4b'1x0z // 4-bit binary. 2nd MSB is unknown. LSB is Hi-Z.

3.14 // Floating point

1.28e5 // Scientific notation

How to use verilog "parameter"

The values of parameters can be overridden during instantiation of leave as default.

Or "defparam" statement can be used for the same purpose.

module myGate ( a, b, c, d );

parameter x = 0;

input a, b;

output c, d;

parameter y = 0, z = 0;

...

endmodule

module top;

reg A, B;

wire C, D;

myGate #(2, 4, 3) m1 (A, B, C, D);

// x = 2, y = 4, z = 3 in instance m1

myGate #(5, 3, 1) m2 (.b(B), .d(D), .c(C), .a(A));

// x = 5, y = 3, z = 1 in instance m2

defparam m3.x = 4, m3.y = 2, m3.z = 5;

myGate m3 (A, B, C, D); // x = 4, y = 2, z = 5 in instance m3

...

endmodule

Friday, August 19, 2016

Verilog CASE statement example with State Machine

module caseExample( input wire clock, input wire resetn, output reg [1:0] state);

`define S0 2'd0

`define S1 2'd1

`define S2 2'd2

reg [1:0] state_nxt;

always @(posedge clock or negedge resetn)

if(!resetn) state <= `S0;

else state <= state_nxt;

always@(*) begin

state_nxt = state;

case(state)

`S0: state_nxt = `S1;

`S1: state_nxt = `S2;

`S2: state_nxt = `S0;

default: state_nxt = `S0;

endcase

end

endmodule